# Distributed Microcontroller Network and Automated Test Harness for the Alaska Research Cubesat

By Gregg Christopher

### Graduate Advisory Committee:

Chair: Dr. Orion Lawlor, Computer Science Members: Dr. Chris Hartman, Computer Science Dr. Denise Thorsen, Electrical Engineering

### **M.S. PROJECT REPORT**

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Computer Science in the Graduate College of the University of Alaska Fairbanks, 2011.

### **Table of Contents:**

Abstract **Project Background Cubesat Picosatellites** Space Systems Engineering Program **Overview of ARC Software Needs** Flight Software Ground Station and Mission Support **Development Environment and Testing Distributed Hardware Architecture** Distributed System Design Subsystem Interface **ARCBus Specification Bus Architectural Overview Expected Error Modes** Single Event Upsets Latchups Traditional Software Error Modes Error Recovery Model **Re-Scoping for MS Project Revised Implementation Scope** Revised Error Discussion Test Bed Design Project Implementation Toolchain Cost Comparison: Hardware Development: Dev Board Design **Physical Assembly** Switching and Control Circuit Firmware Development: Availability of Prior Work and Examples Firmware Structure Selection of a Minimal Command Set Switching Control Circuit Prototype PC Software Development: Serial Communications Switching Hardware Control Simple Automated Test Program Error Observation and Analysis **Observed Error Modes** Methods of Error Measurement Probable Actual Sources of Error Conclusion/Results: Important Lessons Learned Future work References Appendix 1: Physical Layout of Stackthrough Header Pins Appendix 2: Source Code

# Abstract

This project presents the concept, architecture, requirements, design and initial implementation of a distributed embedded network intended for development of a satellite operating system. It includes an analysis of errors expected in the space environment modes of error simulation and methods of recovery. A first proof-of-concept implementation of the development environment and test harness are designed, fabricated and programmed. Sufficient command and data handling functionality is demonstrated to validate using software to induce simulated Single Event Upset (SEU) errors, detect error conditions, and recover via a reset mechanism.

# **Project Background**

### **Cubesat Picosatellites**

The Cubesat standard was initially established by Cal Poly San Louis Obispo as a common mechanical and functional specification that would allow a common launch device to deploy groups of satellites as ancillary payloads to large primary launches. One to three cubical satellites are built with sliding rails fitting this spring-loaded "pod." As of this writing, Spring 2010, 35 cubesats have been launched, several others were lost during a failed launch and the pace of development and launches is growing rapidly. Of special interest to Alaska students is the capability of the Kodiak space port to place cubesats in high-inclination orbits visible to Alaska-based ground stations.

Cubesats are 10 cm on a side and must weight less than 1 kg at launch. They are subject to a variety of safety testing that varies by launch provider. Cubesats must follow appropriate regulations for radio communications.

Since the satellites are small, need not be high-performance, are relatively inexpensive (\$40,000 for development and \$40,000-\$80,000 for launch are current typical costs) and operate in Low Earth Orbit (LEO) where they are shielded from the most severe radiation, cubesats can be a good student project for university aerospace programs.

The Cal Poly cubesat program acts as an intermediary to launch providers by defining standards for satellites and developing cubesat deployment hardware that is pre-qualified for a variety of launch vehicles and providers.<sup>[PPOD]</sup> This allows cubesat builders to bypass the complexities of dealing with the various flight validation requirements of many different potential launch providers by meeting a common standard published by Cal Poly. However, this may mean that in practice, a cubesat developer must be aware and meet both Cal Poly and launch provider requirements if there are other connections such a research grant constraints.

Since the first expected launch opportunity for the Alaska Research Cubesat is through a grant provided by NASA, the UAF program must also pass design review and flight validation testing defined by NASA, above and beyond the baseline cubesat requirements. These requirements also drive UAF cubesat design and implementation processes.

### Space Systems Engineering Program

The Alaska Space Grant supports a Space Systems Engineering group with dedicated lab space and other resources. This interdisciplinary group is currently pursuing its first satellite launch, the Alaska Research Cubesat (ARC). The effort so far has included a graduate course, development of extensive analysis, requirements and design documents and two formal review proceedings before NASA staff.

The full set of documents for the ARC are not publicly available. Presented in this paper is an extremely abbreviated and generalized summary of those requirements.

One goal of this summary is to capture the critical concepts in a very nonspecific form, without including any details that could potentially subject the authors to liability without seeking State Department approval for this paper. Specifics of orbital mechanics, some details of the expected space environment, and other technical details are unspecified, but may motivate some of the project decision and discussion below.

Another goal is to avoid the encumbrance of documentation that would meet more formal NASA requirements,

such as dozens of pages of requirements traceability matrices, large tables of acronyms and references to specific NASA design principle documentation. An attempt is made here to present the end result of the two-year research and design process in as concise and understandable a format as possible.

# **Overview of ARC Software Needs**

Although the primary goal of the ARC project is to launch a functioning satellite, the flight firmware is not the only software development aspect. Satellite work is part of a coordinated effort to create a satellite development and testing lab, space flight hardware and operational ground station for satellite communication. Where the needs of these areas overlap, software effort should be reused to improve integration and avoid duplicate effort.

# Flight Software

The flight software consists of the collected code present on all microcontroller, FPGA and other programmable elements that will be launched on the cubesat itself. A rudimentary operating system will handle communication between subsystems, command and data interfaces, task scheduling and prioritization. Subsystems require software for specific tasks such as radio communication, attitude determination and control and

Space systems have unique reliability requirements. Designing for reliability is critical and special types of system failure must be considered. Physical access to a satellite is impossible after launch, or even after delivery to a launch provider. It cannot be reset with certainty, faulty connections can not be unplugged and reconnected, and aside from also-experimental radio communication system, nothing about the satellite can even be observed directly after deployment. Comprehensive statistics have not been obtained, but between 25% - 50% of successfully launched cubesats have experienced complete failure attributed to the broad category of Command and Data Handling (CDH) error that could be attributed to faulty flight software.

Another key to this process is the realization that reliability engineering can be an endless task and specific risks and failure modes must be prioritized to avoid a bottomless pit of software effort. The ability to reprogram the system in flight is desired, but relegated to a wish list. This will certainly be present on future student or professional cubesats.

### **Ground Station and Mission Support**

The ground station must perform satellite tracking and control of the antenna rotors to establish and maintain uplink and downlink capability. It must also perform proper encoding and decoding of radio signals into data packets, handle packet loss and capture and store received data. There must be a command and control interface allowing mission control to manage the satellite.

Received data is the product of the mission and must be made available for transfer. The ground station system may also be required to perform data interpretation and in order to sensibly automate command and control decisions that are dependent on the content of the data.

Validation testing of the flight software will require at least a representative implementation of the ground station in order to perform end-to-end testing. The ground station itself is subject to reliability requirements, as ground station errors can directly impact the satellite.

There are many Commercial Off-The-Shelf (COTS) choices for ground station subcomponents, including an international effort to create a federated network of ground stations called GENSO<sup>[GENSO]</sup>, led by the European Space Agency and NASA. UAF has been granted an excellent ground station site by NOAA and hopes to make its ground station available for downlink by other cubesat efforts. In particular, a University of Michigan cubesat launched in summer 2010 from the Kodiak private space port.

### **Development Environment and Testing**

Software for development includes collaboration tools, revision control and the toolsets required for specific hardware and programming languages. These are off-the-shelf, but require configuration, training and maintenance to be effective.

In order to perform validation testing, software may be required to automate and log test results. The project will be more adaptable to requirement and design changes as well as last-minute revisions if validation and regression testing are as streamlined as possible. Data logging, warehousing and analysis tools should be considered.

# **Distributed Hardware Architecture**

### **Distributed System Design**

The cubesat consists of discrete subsystems for each of the major system functions. These subsystems communicate via a common interface for command and data communication as well as system maintenance tasks.

In order to reduce overall complexity, each subsystem is required to be as identical as possible. The same microcontroller is used on all subsystems, all have the same electrical connections to the system bus, and the same internal resources are reserved for system tasks. This allows significant code re-use across subsystems and the development of a common codebase for deployment to all subsystems.

### Subsystem Interface

Communication between subsystems prefers well-established serial protocols that have onboard hardware peripheral support. However, lines are reserved to implement custom data protocols, interrupts or a parallel channel. A switched bus also allows access to the hardware programming interface to permit supervisory circuits or in-situ reprogramming with or without a software bootloader.

This interface is physically implemented via stackthrough headers chosen for compatibility with the COTS power system purchased for flight, the Clyde Space power board. Pin assignments are selected to avoid interference with other commercial offerings (such as Pumpkin Space products), in case this or other products desire to mix and match those systems with ARC designs.

The physical arrangement of the pins on the header is located in Appendix 1: Physical Layout of Stackthrough Header Pins.

### **ARCBus Specification**

# Logical Signal Types

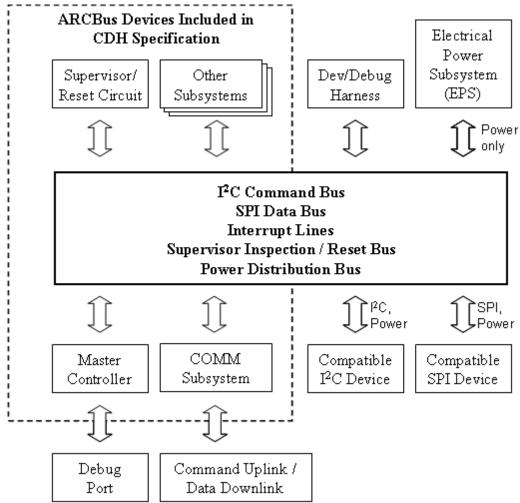

The ARCBus is a collection of data signals grouped into logical functional groups:

- I2C (2 lines): Primarily to exchange commands and responses between components.

- SPI (3 lines): Primarily to exchange blocks of data.

- Programming/Debugging/Reset signals (9 lines): These pins are normally electrically disconnected, but when the enable line for that component is asserted, they allow access to programming, power switch and status reporting functionality.

- Enable Switch Pins (8 lines): Each line is dedicated to enabling the programming pins on one component.

- Power: 5V , 3.3V, Battery Voltage and Ground

### **Bus Architectural Overview**

### **ARCBus Devices:**

ARC Bus Device: Any device that fully implements the ARCBus standard and participates fully in the system. Most ARC components are implemented as ARCBus devices that contain additional circuitry specific to that component.

Master Controller: An ARCBus device that is designated as having the primary task of coordination of command and data flow and maintenance of the system as a whole. This component contains the debug port which allows tethered communication with the satellite after final assembly, but before launch.

Peripheral Adapter: An ARCBus device that exposes the entire system as a peripheral to some external system. For example, the entire ARCBus can present itself as a USB peripheral to a more powerful and complicated mission-specific computer. The external interface to this peripheral may vary, as long as the adapter interfaces correctly with the bus.

Supervisor / Reset Circuit: This circuitry polls the system for error conditions and performs component resets or system resets

### Other Items:

Dev/Debug Harness: This harness consists of cables that expose all signals of the ARCBus while allowing the satellite to be nearly completely assembled. Removal of this harness is one of the last steps to be performed after the satellite has passed all validation tests before the satellite is ready to be shipped.

ARCBus-Compatible I2C and SPI Devices: A non-ARCBus device may be attached to the appropriate signal lines, assuming that it follows certain operational protocols and passes additional tests beyond the requirements specified by the I2C and SPI protocols.

Power Supply: If it is not an ARCBus Device, the power supply must meet the standards to be ARCBuscompatible in order to be connected to the bus.

# **Expected Error Modes**

### **Single Event Upsets**

For the expected space environment and flight hardware, it is expected that ions or radiation will randomly induce electrical charges in the satellite hardware. While this type of event is not expected to damage hardware, it will cause bits in memory to change state randomly. The exact rate of error is extremely difficult to characterize, as it will vary depending on the manufacturing process of a particular device, the orbital details and space weather.

Based on reported conditions of similar satellites and predicted radiation energy levels, these upsets are expected to affect volatile memory only, not the flash memory used for program storage and long-term data storage. Further, it has been indicated that the charge pump circuitry that allows a flash memory write will fail at lower energy levels than those required to overwrite flash. However, since flash memory may be written to programmatically, attention must be paid to any mechanism that could malfunction (or spontaneously be created through stochastic memory changes) in a way to cause flash memory to be written.

For the purposes of this analysis, Single Event Upsets are assumed to be independent and uniformly random across affected memory, though this may not be true based on details of actual hardware used. Although the error mode is named the "Single" Event Upset and they are expected to occur sequentially as a poisson process, the analysis and mitigation of these events must assume that many could occur undetected before

any observable change in state. A detected error state may include an arbitrary amount of corrupted memory and the possibility that some of it has been written to less volatile storage.

### Latchups

A latchup event is one where a temporary electric structure is formed that causes a transistor to short to ground. This is typically caused by excess current and causes memory or a logical structure to be stuck in one state. There is no way to resolve this in software and the system must be powered down in order to clear the latchup. In some circumstances, a latchup can cause a risk of overheat from excessive current through an element. In the vacuum environment, cooling may be impaired, increasing the need to detect and clear this condition promptly.

Latchup events are much more difficult to emulate using the software-only techniques available for this project. A recovery method is provided by the power reset capability of the supervisory circuit, described below. Provisions for future work in testing and recovering from latchup events are included in the project implementation.

### **Traditional Software Error Modes**

In addition to the special demands of the space environment, any software project is subject to the usual range of error modes. The design, development and testing processes must account for detection and recovery of errors induced by faulty programming or unexpected operational circumstances that induce soft errors in the satellite. This places additional emphasis on the need for the recovery mechanisms to be well thought out, simple, robust and thoroughly tested.

### **Error Recovery Model**

The complete error recovery model for the satellite is based on first attempting soft recovery of known corrupt memory before performing a hard reset, and on first attempting to reset a single subsystem before resetting the entire satellite.

The desired order of recovery options is:

- 1. Per-subsystem soft error recovery. This would encompass scenarios where redundant memory storage or checksum-based approaches are sufficient to detect and recover from an error without any interaction with other subsystems. This might also include checking register states, such as those that control peripherals, against known correct values in non-volatile memory.

- 2. Guided recovery by external commands over the shared bus. This would require that all subsystems involved have working methods of communication, but would allow them to compare state information to attempt recovery.

- 3. Self-reset on command by bus master. Assuming that communication remains possible, an error has been detected, a subsystem can be ordered to perform a soft-reset. This is expected to resolve many non-latchup error modes, in cases where the reset capability has not been compromised.

- 4. Hard reset of subsystem(s) by the supervisor circuit. The supervisor circuit has a dedicated communication line to each subsystem. It can query each, and assuming that a sufficient majority analysis has been reached as to which subsystem is in error, that subsystem can be selectively reset.

- 5. Hard reset of the entire satellite by the supervisor circuit. This is expected to be highly likely to recover from a broad range of errors, as it allows power to be completely drained from all programmable elements. This reset is likely to be common in any case where communications have been interrupted,

since the subsystems would be unable to compare information that could lead to a diagnosis of a single malfunctioning subsystem. In particular, since the serial channels are shared, any subsystem with malfunctioning peripheral behavior is likely to induce this error recovery step.

# **Re-Scoping for MS Project**

The discussion of goals and requirements above describes a system that may be infeasible to develop in the scope and context of a single Master's thesis. In a perfect world, this paper would present analysis of a finished and flight-ready set of software systems, but that goal proved unrealistic for the available time and resources. Additionally, the extent of Waterfall-style design work for the Cubesat has a tendency to encounter analysis paralysis that can be improved by smaller-scale, earlier development. With guidance from the graduate project committee, the scope of this project was restated to create an achievable first step that would also usefully contribute to the development of a satellite.

### **Revised Implementation Scope**

With advisory guidance, the following goals were identified as most desirable while still being achievable within the scope of a Master's Thesis project. These were chosen to further the needs of the ARC project as a whole while still providing a defined "end point" to a project that could be arbitrarily large.

- The system should demonstrate the ability to exchange commands between subsystems, perform work based on those commands and respond with the result of the commands. Those commands should have clearly defined outcomes that can be tested for correctness. Each subsystem should be able to accept commands, report results, and be interrogated for status information by an external control and testing interface.

- Software simulation of error modes should be demonstrated on command, in such a way that errors are repeatable as representative of expected error modes as possible.

- The system should allow for manual and automated testing. This capability should primarily take the form of easily-modified PC software that can server both as the primary test control mechanism and the basis for a future test harness for more sophisticated testing and analysis.

An attempt was made to defer resolution of certain categories of work:

- Work on a complete command table able to handle all operations of the satellite, including mission

phase management and specific subsystem operations. Though highly desirable, this is an unrealistic

goal until a basic concept and framework have been proven to work.

- Complicated command interactions requiring queueing or prioritization logic. In the absence of subsystem prototypes, procedures of this type are likely to see many revisions up to and through the completion of this more limited project.

- Anything requiring more hardware development should be deferred. Due to unresolved limitations in the first iterations, some rapid-prototyping of hardware was required to reach functionality.

### **Revised Error Discussion**

The revised scope is still adequate to test SEU and most firmware error modes, but does not have any direct provision for testing latchup. It is sufficient to test the complete sequence of planned error recovery methods with only software modifications. Other than those constraints, the revised scope does not impact the analysis of error causes, failure modes, or recovery methods.

### **Test Bed Design**

Since the supervisor circuit has not been designed, the implementation of this project will serve as the first prototype of the physical and logical operations that system must perform. The final form of the test harness will be the three available dev boards connected to a prototype control circuit that will stand in as the supervisor circuit. That circuit will in turn be connected to a PC that will host software controlling the entire test harness, emulating each dev board sufficient to test it, and performing control logic that is not yet present on the supervisor circuit.

# **Project Implementation**

The implementation of this project consists construction of physical hardware, firmware for programmable elements of the hardware, and PC software. This project involved requirements, design and review aspects before any code could be written. These were required by the Space Grant before hardware design could commence and were a non-negotiable blocking factor to further development. The background and design sections above are a condensed summary of subsections of the requirement and design specifications produced during this process. Analysis of risk and timelines were also required, but are omitted from this report.

The interactive portion consists of three programs:

- An off-the-shelf serial communication tool, realterm.

- A tool to control the switching hardware and power supply.

- A programming framework to perform ad-hoc serial communication.

The automated portion of the test harness is constructed using components from the switching control program and the serial communication libraries. Since the libraries used happen to compile cleanly when used together, they are included in a single project. Communication code is included that allows the project to be broken out into multiple executable objects with messages passed between them in case incompatible libraries are adopted or precompiled tools are added to the system.

### **Toolchain Cost Comparison:**

Choosing a compiler and debugger combination for embedded development may not be trivial. At the outset of this project, despite exhaustive testing, no working combination of compiler, hardware programmer/debugger and drivers was found for the 64-bit Windows environment on development machines, so the entire toolchain was run in a virtualized environment. While eventually feasible, this introduced another layer of difficulties. Eventually TI released improved drivers and compatibility improved.

Four compiler/debugger suites were considered for this project, included based on the fundamental criterion that the experimenter was able to get each of them to function at all.

mspgcc: gcc toolchain for MSP430

- + Free

- + Unlimited code size

- + One team member experienced and familiar with usage

- Most of the team were unable to effectively use the gdb debugger

- Unique precompiler conventions. Example code is unlikely to work.

### IAR Embedded Workbench

- + Extremely commonly distributed

- + Reasonably simple build and debug process

- + Plentiful code examples for beginners

- code size limit

- "Request Quote" price for version with sufficient code size

- TI Code Composer Studio (CCStudio)

- + Developed by device manufacturer with direct support

- + Reasonably simple build and debug process

- + Manufacturer provides code examples

- code size limit

- \$795.00 per seat for version with sufficient code size

### **Rowley Crossworks**

- + Reasonably simple build and debug process

- + One team member experienced and familiar with usage

- Unique precompiler conventions. Example code is unlikely to work.

- code size limit

- + \$150/seat personal noncommercial license available

Based on the difficulty in using mspgcc and the prohibitive cost of the other two options, Rowley Crossworks was selected as the compiler and debugger software. To ensure broad compatibility, the TI FET programmer/ debugger hardware was chosen, but competing commercial and open hardware alternatives are rapidly evolving and should be monitored for maturity.

### Hardware Development:

This project included participation in the requirements, design and fabrication processes of prototype hardware. From the first statement of requirements, roughly 18 months elapsed before a first iteration of hardware was in hand and usable for development. This was by far the most time-consuming aspect of in this project, though outside the scope of this report.

### **Dev Board Design**

The initial goal was to produce a simple, experimenter-friendly carrier board for rapid prototype development. This "dev board" includes most of the common hardware elements that each subsystem of the satellite is intended to share, plus extra components such as a serial communication bridge, breakout areas for microcontroller pins, indicator lights, and jumpers to choose between optional hardware connections.

The schematic and layout of the dev board have not been approved for public release and can not be included here. They are considered proprietary information by the Alaska Space Grant, but might be made available on request. Please see contact information at <u>http://spacegrant.alaska.edu</u> for more information.

Given that these designs are simplistic by most industry standards, this may seem unusual to many readers, but this closed mode of development seems common in space systems engineering projects. This may be due to a combination of fear of United States arms trafficking laws and a lower level of penetration of open source methodologies that are more widespread elsewhere in academics. A desire to exert control over how these designs are represented and potentially reused has also been expressed.

### **Physical Assembly**

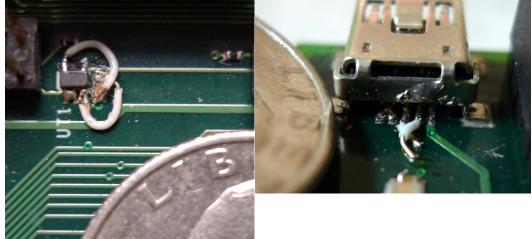

Several parts and layout combinations in the dev board were especially small, and beyond the ability of anyone not expert in soldering. Because of this, a pick-and-place machine and reflow oven were required for board assembly. While the vacuum head and high-zoom cameras allow for precise and highly reliable assembly, these techniques are extremely slow and require a trained, careful and focused operator. The number of dev boards created is far fewer than hoped and they have not yet filled their potential as a commonly used prototyping tool.

Detail image of dev board components.

One consequence of the waterfall-style (described as the "V Model"[VMODEL]) development methodology was that the first revision of the dev board was purchased in bulk, and instead of correcting errors discovered in the first version and purchasing corrected circuit boards, tiny jumper wires are soldered manually for every dev board produced. A few of the jumper soldering jobs have been accomplished only by the author and the lead Electrical Engineer on the project.

Detail images of wire jumper corrections.

Complete dev boards are designed to interconnect using stackthrough headers, identical to those that will be used in the final satellite assembly. However, this method of connection is both extremely high friction and difficult to disconnect, and leaves little to no room for physical access to the prototyping areas of each board.

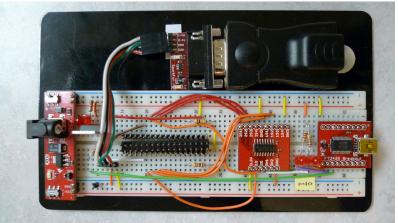

A side-by-side layout would be much more usable for prototyping and testing tasks. Commonly available ribbon cable connectors are sufficient for connecting the boards, but the dev boards are not laid out in a way conducive to this arrangement. Given the other demands on the time of other project members and the extremely long turnaround on board design, requesting a change to the dev boards or an extra board was infeasible. To overcome this, simple carrier boards were designed using freeware schematic and layout software and etched to bare copper boards using toner transfer methods. This rapid prototyping capability proved to be essential to overcoming bottlenecks in the availability of hardware development resources on the project.

Hand-etched carrier circuit board connecting a dev board to the ribbon cable.

### **Switching and Control Circuit**

The Supervisor Circuit that will manage power resets for error recovery. A prototype of the final circuit has not yet been developed, so a temporary stand-in is required to fill these functions for the test harness.

Use another dev board for the circuit, using the peripherals on the dev board for communication channels and general-purpose I/O pins to control power switching and multiplexed communication channels. This would have the advantage of being able to re-use code from the firmware from the other dev boards. If the dev boards weren't so difficult to populate and solder corrective jumper wires, this would have been the most attractive option.

Use another microcontroller break-out board and breadboard to create the circuit. This could be another MSP430 or another convenient chip. This could potentially be simpler than using a complete dev board, but offer fewer reuse options.

Use off-the-shelf parts that specialize in the required capabilities and do not require firmware. This offloads potential complexity to PC software, but reduces the time invested in embedded development. For the initial test harness, this option was chosen as the requiring the most minimal time investment.

Control Circuit Prototype with COTS Parts

### Firmware Development:

One portion of this project was to develop firmware for the ARC development boards using the MSP430F2618 microcontroller. This firmware serves as a proof-of-concept and exploration of basic methods that will serve as the groundwork for future satellite development.

### Availability of Prior Work and Examples

Unlike many programming projects, a simple internet search is unlikely to turn up adequate example code for a particular problem. Reference examples provided by hardware manufacturers and compiler vendors tend to be extremely simplistic, because more complicated examples lose general applicability or may not be approachable. Even if references are found for a particular microcontroller line, they may be for a different serial peripheral, work only with one compiler, or use peripherals in a different context.

The best available resources tended to be other students or professors. It is possible that the accumulation of experience with this development environment can lead to better knowledge transfer for future students. However, given rapid changes in microcontrollers, most current code faces a significant risk of obsolescence even in the short term.

This challenge indicates a greater need for more frequent development iterations, more exchange of information between team members and more testing. The best immediate response to this observation is to communicate it back to the team to be included in risk, cost and time estimates.

### **Firmware Structure**

The firmware is intended to eventually be a model for Cubesat flight firmware, so an initial goal is to use as few resources and introduce as little complexity as possible. The firmware model can be roughly divided into four categories:

- Initialization and configuration of memory and registers, especially the control registers for peripherals and associated interrupts.

- Interrupt handling routines.

- Utility functions for routine operations, including peripheral management.

- A main event loop.

If possible, all of the configuration settings required to use a peripheral in a given mode are collected into one place and structured in such a way that they can be mixed and matched for different needs. Some peripheral-handling functions, such as the UART routines, are at a high level of maturity and have been broken out into separate header and source files for group use. Others, such as the I2C handling routines, are not yet good enough to redistribute in any finished form.

The interrupt handling routines cannot be as easily encapsulated, as the same vector may be used by multiple peripherals in varying states. Interrupts are kept as minimal as possible, reading or writing to predefined dedicated memory buffers and setting a flag for the main loop to later handle further processing. One unresolved issue with peripheral interrupts is the resolution of error and wait states. At present, the team has not yet settled on best-practice principles for these situations.

Each peripheral requires interface code to be written along with appropriate data structures. Additionally, a few simple functions are provided to create testable capabilities and as a stand-in for eventual mature satellite development. These structures are responsible for managing the state of each peripheral and the state of the microcontroller as a whole.

Finally, an extremely simple main loop handles flags raised by communication peripherals or timers. Display LED states are managed here, as well as processing actions that must occur in a specific sequence, such as sending a command to another board via I2C after external communication has been received via UART. Commands and external communication can be triggered asynchronously from within the main loop as well.

### Low-Power Modes

The current firmware implementation does not take advantage of low power modes because of the complexity of potential interactions between multiple peripherals operating simultaneously. Each would need to manage its own set of registered interrupts for leaving low power mode without disabling the set required for the others. This test harness does not yet include a power minimization component.

With correct power management, MSP430 power consumption tends to be linearly proportional to the speed of the microcontroller and the amount of time spent in operation. This makes it possible to "pay as you go" for uC power. One satellite engineer at the 2009 Cal Poly Cubesat workshop advised against over-analysis of this area, though. If there is a 5 watt transmitter module in operation, the relative gain from saving micro- or milliwatt consumption of power can be insignificant.

### **Standard Libraries**

To the surprise of this investigator, mature and reliable implementations of many ANSI C libraries were provided with the CrossWorks compiler. Once appropriate low-level supplementary code had been written, such as a putchar() implementation, relatively complicated tasks such as string handling and formatted output could be written using familiar language constructs. These libraries would work (in theory) even on the lowerend microcontrollers in the MSP430 series, provided enough memory space. This may be a common and expected experience for experienced embedded developers, but for a computer scientist unfamiliar with the product, it was a welcome discovery.

### **Selection of a Minimal Command Set**

One goal of the project firmware was to perform actions representative of the actual tasks that satellite subsystems will perform. A small set of commands were chose for this purpose.

The command set for the test harness firmware should be as minimal as possible while still demonstrating the ability to:

- Demonstrate basic responsiveness.

- Store and retrieve arbitrary sets of data.

- Demonstrate communication between development boards.

- Exchange data between boards.

- Demonstrate the ability to act on commands sent between boards.

- Perform work on command.

- Simulate single-event-upset events on command.

Assuming that the firmware can

The command set used for test runs and observations of error rates was:

| Command                                  | Action                                                                                                                                              |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Set LED Pattern                          | Immediately change the indicator light pattern variable and update the port controlling the indicator lights.                                       |

| Read LED Pattern                         | Report the value of the indicator light pattern variable.                                                                                           |

| Remote Set LED                           | Send a command over the bus to a specified board to set its LED pattern.                                                                            |

| Set Work Area Buffer Segment             | Set the contents of the specified portion of the data buffer.                                                                                       |

| Read Work Area Buffer Segment            | Report the contents of the specified portion of the data buffer.                                                                                    |

| Perform Calculation on Buffer            | Perform a predetermined calculation on the entire data buffer.                                                                                      |

| Send Buffer Segment to Other Board       | Send a segment of the data buffer with a given offset and length to another board.                                                                  |

| Flip Bits (Intentionally corrupt memory) | Intentionally corrupt volatile memory by performing<br>an XOR of the designated location with a bit mask.<br>Typically used for one bit at at time. |

### Switching Control Circuit Prototype

The switching control circuit serves as both a test harness and as a stand-in for the Supervisor Circuit that will be responsible for restoring the satellite when errors are detected. Three options for creating this circuit were

considered:

- Use another dev board for the circuit, using the peripherals on the dev board for communication channels and general-purpose I/O pins to control power switching and multiplexed communication channels. This would have the advantage of being able to re-use code from the firmware from the other dev boards. If the dev boards weren't so difficult to populate and solder with corrective jumper wires, this would have been the most attractive option.

- Use another microcontroller break-out board and breadboard to create the circuit. This could be another MSP430 or another convenient chip. This could potentially be simpler than using a complete dev board, but offer fewer reuse options.

- Use off-the-shelf parts that specialize in the required capabilities and do not require firmware. This

offloads potential complexity to PC software, but reduces the time invested in embedded development.

For the initial test harness, this option was chosen as the requiring the most minimal time investment.

Fortunately, the FT245<sup>[FTDI]</sup> device drivers proved easy to use.

### PC Software Development:

### **Serial Communications**

In the Windows en environment, there are a large number of serial libraries and tools available. For this project, a serial library that is simple to use, free and that works with all of the hardware drivers in use has not yet been identified. An ideal candidate would also be open-source.

The current library, CSerialPort<sup>[CSERIAL]</sup>, is not the ideal choice because it does not work with all of the virtual com port drivers in use elsewhere, but it was sufficient for the initial test harness implementation.

### **Switching Hardware Control**

The switching hardware control relied on PC software-controlled GPIO pins provided by the Fortunately, the manufacturer provided libraries were easy to use and easy to integrate with the other portions of the codebase. A simple console-based program was produced to control the multiplexing of serial communications and the power reset. This program can be used either interactively or by passing control characters to its input stream.

### Simple Automated Test Program

Automated test case generation is fairly straightforward. Commands can be sent according to a pre-generated list or generated randomly, with or without a fixed seed. First, the switching control hardware is instructed to connect to a specified dev board. Then the command is sent via the serial interface and the harness enters an idle mode for a fixed time period. If no acknowledgement is received from the targeted board, then it is assumed to have entered a fault state and a reset is performed.

A data structure records the expected state of selected memory on each microcontroller so that the test harness can maintain an independent simulation of the satellite function. This facilitates both to validate SEU simulation and as a software debugging mechanism. This mechanism allows unit testing of individual subsystems and regression testing against known good previous system configurations.

Some commands exist primarily to induce and check for error states. Based on a model of the addressable satellite memory, bits to flip are chosen to simulate SEU errors. Currently this model is uniformly random, but may be informed by more extensive analysis of error distributions in the future. For example, SEU upset of

control channels could result in errors concentrated in some area of memory.

The test harness collects the responses from subsystems to each command and summary statistics of command results. As useful metrics are developed to express satellite functionality, these recorded results are expected to increase in usefulness.

# **Error Observation and Analysis**

### **Observed Error Modes**

Aside from recoverable errors in the reported data buffers, by the most commonly observed error mode was that the embedded network becomes non-responsive. This condition is extremely difficult to automatically diagnose. Human intervention is required at that point to attempt to characterize the error. A hardware debugger may be attached to one of the microcontrollers, but it is possible that timing-dependent behaviors may occur differently in that case. In many cases, whether an error mode is attributable to a bit flip event or an inherent weakness in the firmware implementation is an open question.

### **Methods of Error Measurement**

In the absence of methods of soft recovery from errors, each experimental run terminates at the point where the system fails to respond to further commands and must be reset.

Because the test harness in this project represents a point in time for the cubesat development, the actual numbers produced are far less valuable than its contribute to implementation and debugging. As the satellite firmware reaches maturity across several components, these metrics will be tuned to expected upset rates for the space environment and become the primary measurement of expected satellite performance.

The test harness records:

- Number and type of commands sent until failure.

- Number of simulated SEU disruptions until failure.

- Distribution of commands sent, summary counts and command sequence.

- Approximate temporal distribution of commands, to selectively force command queueing, conflicting or dependent command resolution and other time-dependent conditions.

### **Probable Actual Sources of Error**

Errors were mass-produced intentionally by the testing process. For a relatively immature research product such as this project, it is reasonable to conjecture that other sources of error occur, mixed in with the intentionally simulated results. The bulk of errors were not investigated individually. A random sampling of observed errors were analyzed and a rough characterization of observed error categories follows:

### Induced Errors

### Known Firmware Weaknesses

• At the time of this project, some elements of the serial peripheral firmware implementation are known to be incomplete or lack appropriate error handling. This became especially apparent during higher-speed testing where the microcontrollers would be expected to be forced to wait or arbitrate use of the shared

bus.

- The serial peripherals were intentionally configured to run at much less than their maximum speed (50 KHz or less). This was done to ease diagnosis with inexpensive logic analyzer hardware as well as reduce the chance of signal integrity issues due to long wires in the test bed. However, this also introduced much more frequent bus collisions and artificially long waits for the microcontroller CPU while the serial peripheral completed a transaction. These combined tended to exaggerate the impact of weaknesses in the interrupt and state handling.

- This is one of several ways in which the value of the automated testing harness is demonstrated, as can is difficult and tedious to manually test issues such as these.

### Firmware bugs

• This project does not represent a mature, commercially viable level of reliability, much less the extreme reliability required for space operations. It is reasonable to expect that undiscovered bugs in the initial firmware contribute significantly to observed error rates. Given the frequency at which government and commercial projects experience errors that are either uncategorized or lumped in the general category of "software malfunction," the ability to load-test candidate systems and expose these errors may be of greater value to the success of the project than the stated purpose of simulating single event upset errors.

### **Control Hardware Timing and Stability**

• The control hardware appeared to have some switching latency, which may be related to the relatively crude breadboard techniques or poor understanding of proper electrical design for the components used. It was possible to induce a higher rate of error by shortening the wait to send or receive signals after switching the control circuitry to address a different board.

### **UART Errors**

• The frequencies used by the microcontroller peripheral and USB-to-UART bridge chip are approximate, sometimes off by as much as one to three percent. This depends on such factors as compromises in clock and peripheral configuration and factory calibration of the microcontroller. Simple software measures such as sentinel values to reject noise and checksums were employed, but a thorough analysis of UART-induced error was not performed.

# **Conclusion/Results:**

This project included extensive group and individual work aimed at both arriving at the first implementation of the satellite test and development harness and at the larger goal of successfully flying UAF's first satellite. It would have been far easier to produce a project like this one individually, without requirements for design review proceedings for any major decision or document and without producing the extensive and proprietary requirements and design documents required for NASA review and to meet the Space Grant goal of preparing students to work in the government and commercial aerospace fields.

At the inception of this project, no software or hardware architecture had yet been evaluated and all major technical decisions leading up to its present state had to be researched and evaluated. This project included creating and promoting the concept of the development boards and their original statement of requirements. It included participation in the design and layout review process for them as well. Nearly all analysis of expected error modes and planning of recovery mechanisms was left up to this project to plan and complete.

Because the Space Grant did not provide any hardware that could be used for development or presentation,

parts were sourced and purchased out-of-pocket. Once purchased, fabrication of the dev boards was up to the individuals who needed them, so the requisite tools were learned and three boards were fabricated and tested.

Only after all of this work was completed could any substantial software be written. Because a development environment was not yet available, programming hardware, a compiler and other parts and tools such as a logic analyzer were also purchased and incorporated into the test harness capabilities.

The firmware test bed successfully demonstrated all of the intended commands in interactive testing with and without debugging hardware attached. One important discovery was just how easily failure can be induced in a stress-test of not-yet-mature firmware. Though familiar to the engineering department at UAF, resources on how to develop extremely highly reliable software for the MSP430 processor were difficult to obtain. Even the most senior and knowledgeable team members had only a vague concept of how to properly implement I<sup>2</sup>C communication, and that task was part of this project.

# **Important Lessons Learned**

- Design for ease-of-prototyping. The smallest possible components, tightly packed, might be optimal for a production design, but are hardest to reliably assemble. Including too many capabilities in a single, non-modularized unit only multiplies the number of things that can go wrong and the difficulty of diagnosis when something does go wrong.

- Many modern software engineering methodologies have not reached broad adoption in some areas of aerospace engineering. Interdisciplinary developers must take care to understand the perspective that all team members will bring to the design process.

- The final Cubesat software as specified for the Alaska Research Cubesat will require significant effort to achieve completion and reliability. This may sound like a trivial observation, but this project revealed an interesting way to assess project effort. by choosing one aspect of the project, and pursuing it in depth independent of other aspects, a more full understanding of the complexity and difficulty can be acquired. This understanding may translate usefully to other parts of the project. This also suggests an interesting general method of effort and cost estimation, by picking a narrow "slice" of the available work and pursuing it alone to a higher level of maturity than the rest of the project, the probably effort required for related work can be more accurately estimated!

- The kind of prior work and examples that are commonly assumed to be available for many software development projects may be significantly less extensive or harder to find for embedded or aerospace projects.

- Automated testing can reveal errors in firmware that are difficult to detect even after many hours of interactive, human-driven testing.

# **Future work**

- 1. Merge the test firmware code with work done by other team members and converge as quickly as possible on a shared code base for future development.

- 2. Continue work on all of the highest priority satellite Command and Data Handling tasks, such as a more complete command set, a final framework and code base for the firmware, and many other needs.

- 3. Once the simulated single-event upset methods have achieved a high level of confidence, experiment with locally available sources of radiation to see if upset events can be induced and whether the resulting error modes substantially agree with those produced in software.

- 4. Identify a better serial communication library or toolset for the PC software. This turned out to be

surprisingly difficult challenge in the Windows environment. Serial communication has become a niche capability with a surprisingly error-prone field of tools. It seems simple at first to just invoke UART as a communication channel, but it might be worthwhile to reconsider it in favor of USB serial communication for future work.

5. Start testing real satellite subsystems in preparation for a trip to space!

# **References and Related Links**

[PPOD] Jordi Puig-Suari, Clark Turner, William Ahlgren, "Development of the Standard CubeSat Deployer and a CubeSat Class PicoSatellite" Retrieved 11/30/2011: <u>http://www.cubesat.org/images/Papers/</u> cubesat\_paper.pdf

[GENSO] GENSO introduction: http://www.genso.org/

[ITAR] International Traffic in Arms Regulations: http://en.wikipedia.org/wiki/ITAR

[CSERIAL] CSerialPort v1.27 An MFC class for Win32 serial ports: http://www.naughter.com/serialport.html

[VMODEL] V-Model: http://en.wikipedia.org/wiki/V-model

[FTDI] Future Technology Devices International Ltd: FT245R - USB FIFO IC: <u>http://www.ftdichip.com/Products/</u> ICs/FT245R.htm

I.Galysh , K. Doherty , J. McGuire , H.Heidt , D. Niemi , G. Dutchover, "CubeSat: Developing a Standard Bus for Picosatellites" Retrieved 11/30/2011: <u>http://www.cubesat.org/images/Papers/stensat\_hist.pdf</u>

Ryan Nugent, Riki Munakata, Alexander Chin, Roland Coelho, Jordi Puig-Suari, "The CubeSat: The Picosatellite Standard for Research and Education" Retrieved 11/30/2011: <u>http://www.cubesat.org/images/More\_Papers/cps2008.pdf</u>

Alaska Space Grant Program: http://spacegrant.alaska.edu/

The CubeSat Project: http://www.cubesat.org/

Rowley Associates, CrossWorks for MSP430 - C Compiler for MSP430 Microcontrollers: <u>http://www.rowley.co.uk/msp430/</u>

MSP430 Microcontroller - Texas Instruments: <u>http://www.ti.com/lsds/ti/microcontroller/16-bit\_msp430/</u> overview.page?DCMP=MCU\_other&HQS=Other+IL+msp430

# **Appendix 1: Physical Layout of Stackthrough Header Pins**

| Pin Des<br>I2CCL<br>I2CCL<br>MISO<br>MOSI                                                                                                                                                                                                                                                                | 4 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | Header 2 EN0 EN2                 | 2    | EN1                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------|------|------------------------------------------------------------------|

| der 1 Pin Desig<br>I2CCLK<br>I2Cdat<br>MISO<br>MOSI                                                                                                                                                                                                                                                      | 6 NTMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                 | Ξ                                |      |                                                                  |

| Pin Desig<br>I2CCLK<br>I2CCLK<br>I2Cdat                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>.</u>          | $\sim$                           | 4    | EN3                                                              |

|                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5 °               | EN4                              | 6    | EN5                                                              |

|                                                                                                                                                                                                                                                                                                          | ğ ∞ k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | , RC              | ENG                              | •    | EN7                                                              |

| 9<br>Cloc<br>Cloc<br>Data<br>SPI [<br>SPI [<br>Mast                                                                                                                                                                                                                                                      | 8 10 12<br>100/11 P1 0 P1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9                 |                                  | 3    |                                                                  |

| 9     11     13     15     17     19     21       nations     2C Command Bus Signals       2C Command Bus Signals       Clock Signal for the I2C command bus       Data signal for the I2C command bus       SPI Data Bus Signals       Master-In, Slave-Out SPI line       Master-Out Slave-In SPI line | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 1               |                                  | 12   |                                                                  |

| 13<br>13<br>13<br>14<br>15<br>11<br>16<br>17<br>11<br>16<br>17<br>11<br>16<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17                                                                                                                                                 | P1 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2<br>5<br>1       |                                  | 14   |                                                                  |

| 15<br>Sign<br>the I2<br>Out S<br>-Out S                                                                                                                                                                                                                                                                  | P1 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                |                                  | 16   |                                                                  |

| 17<br>C con<br>C com<br>SPI lin<br>SPI lin                                                                                                                                                                                                                                                               | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |                                  | 18   |                                                                  |

| nmand t<br>e e                                                                                                                                                                                                                                                                                           | 18 20 22 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 19 21          |                                  | 20   |                                                                  |

| d bus                                                                                                                                                                                                                                                                                                    | SPICI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21                | TORQ                             | 22   | TORQ                                                             |

|                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                | TORQ TORQ 5V                     | 24   | TORO TORO 5V                                                     |